[위기 맞은 네패스그룹]전사 올인한 차세대 패키징 공법, 기술절벽 '위기감'①'FO-PLP' 변형·휨 난제, 상반기 퀄컴 계약해지 통보 '직격탄'

조영갑 기자공개 2023-11-07 07:59:17

[편집자주]

국내 주요 후공정 외주가공(OSAT) 업체인 네패스그룹이 전사적 위기를 맞고 있다. 지주사격인 네패스를 중심으로 차세대 패키지 기술 '팬아웃패널레벨패키지(FO-PLP)' 공정에 '올인' 했으나 양산 페이즈 진입에 실패하면서 활로를 찾지 못하고 있어서다. 내년 패키징 시장의 업사이클이 예고된 상황이지만, FO-PLP 승부수를 계속 던질 수 있을지 불투명하다. 네패스그룹의 그간 궤적과 돌파구를 조명해 본다.

이 기사는 2023년 11월 03일 13:23 thebell 에 표출된 기사입니다.

"기술적 완성도가 농익지 않은 상황에서 너무 성급하게 샴페인을 터뜨렸다."한 여의도 기관투자자가 네패스그룹의 '팬아웃패널레벨패키지(FO-PLP)' 공법을 두고 한 말이다. 2020년부터 본격적으로 FO-PLP 기술에 투자를 확대하기 시작한 네패스그룹은 지난해를 기점으로 계열사 '네패스라웨'를 축으로 놓고, 양산 라인에 진입하기 위해 그룹 전사 역량을 집결시켰다. 지난해 하반기부터 글로벌 톱티어 팹리스 고객사 대량 수주에 임박했다는 소식도 돌았다. 반도체 업계 전체가 네패스의 행보를 숨죽여 지켜봤다.

하지만 네패스그룹은 장기간의 고객사 퀄(품질인증) 테스트에도 불구하고, 고객사로부터 계약해지 당하는 수모를 겪으며 신규 시장 창출에 실패했다. 결과적으로 FO-PLP의 기술적 난이도와 수율 문제를 극복하지 못한 탓이다. 더욱 뼈아픈 것은 FO-PLP를 통해 TSMC-ASE의 아성을 넘으려 했던 삼성전자 역시 FO-PLP의 한계를 인정하며, 항로를 변경했다는 점이다. 삼성전자와 동맹노선을 구축하고, FO-PLP에 막대한 투자를 단행한 네패스그룹으로서는 진퇴양난의 형국인 셈이다.

◇네패스 축 삼아 턴키 프로세스 구축 '올인'

네패스그룹은 수년 간 반도체 후공정 패키지 분야에서 '토탈 밸류체인'을 구축하기 위해 노력해 왔다. 웨이퍼레벨패키지(WLP) 범핑을 전문으로 하는 지주사 격 네패스를 정점으로 웨이퍼 프로브 테스트(Probe Test)와 파이널 테스트를 수행하는 '네패스아크', 이를 최종적으로 FO-PLP 방식으로 패키징하는 '네패스라웨' 등으로 사업 영역을 확장했다. 2차전지용 리드탭을 생산하는 '네패스야하드'도 주요 계열사다.

2분기 말 기준 각 사업부문이 총 매출액에서 차지하는 비중은 △WLP Bumping 외(네패스) 51.06% △웨이퍼 테스트(네패스아크) 25.19% △FO-WLP(네패스라웨) 7.37% △2차전지용 리드탭(네패스야하드) 15.18% 등이다. 2차전지를 제외한 반도체 영역에서 백엔드 어셈블리, 테스트, 패키지가 모두 가능한 후공정 턴키 프로세스를 구축하고 있는 모양새다.

여기서 핵심 기술이 네패스와 네패스라웨가 주축이 돼 개발, 수행하고 있는 FO-PLP 공법이다. 네패스는 삼성전자 등의 물량을 받아 기존 WLP(웨이퍼레벨패키지) 공법으로 범핑, 패키지를 수행하고 있었지만, 2020년부터 본격적으로 팬아웃(Fan-Out) 기술을 토대로 패널레벨패키지(PLP) 공법의 애드벌룬을 띄워왔다. 같은 해 2월 FO-PLP 사업 부문을 물적분할해 이를 전담할 네패스라웨를 신설했다.

FO-PLP를 논하기 위해서는 대만의 TSMC와 ASE를 빼놓고 설명하기 힘들다. 애플의 최대 고객사이기도 한 TSMC는 이른바 FO-WLP(팬아웃 웨이퍼레벨패키지) 기술을 토대로 삼성전자와의 패키지 전쟁에서 승기를 잡았다. 이 기술을 내세워 애플의 AP 파운드리 물량을 대거 선점할 수 있었기 때문이다. ASE 역시 대만에 본사를 둔 글로벌 톱티어 OSAT 기업이다. TSMC와 손잡고 비메모리 후공정, 패키징을 수행한다. 삼성전자와 네패스의 관계를 떠올리면 쉽다.

한때 FO-PLP가 극복해야 할 기술이라 평가됐던 'FO-WLP' 공법은 웨이퍼 상에서 전극을 형성하는 방식으로 다수의 다이(Die)를 동시에 여러 개 패키징하는 기술이다. 기존 전통적인 패키지 방식은 웨이퍼 위에서 반도체 제작이 끝나면 다이를 모두 분할해 각 다이마다 일일이 패키징했다. 웨이퍼 위에서 한번에 패키지한 후 다이싱(분할)하기 때문에 전통 방식 대비 생산효율이 월등히 높다.

여기에 TSMC와 ASE는 기존 칩 안에 입출력 단자를 배치하는 팬인(Fan-In) 방식이 아닌 출력 단자의 배선을 칩 바깥으로 뺀 '팬 아웃' 방식으로 더 넓은 면적에서 입출력단자를 활용할 수 있게 했다. 팬아웃 방식은 배선을 칩 외부에서 배치할 수 있기 때문에 칩 면적 보다 더 많은 수의 단자를 활용할 수 있고, 결과적으로 칩의 성능을 더 개선하는 방식으로 평가된다.

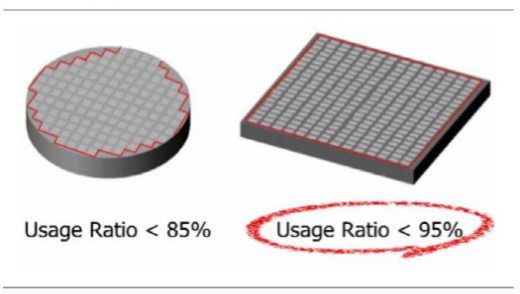

네패스그룹의 FO-PLP은 팬아웃 방식이라는 점은 TSMC와 동일하다. 하지만 여기서 한발 더 나간다. TSMC-ASE가 8인치(200mm), 12인치(300mm) 원형 기판(Substrate)을 사용하는 데 비해 네패스는 600mmX600mm의 대형 '사각형' 패널을 기판으로 놓고, 패키징을 하는 방식이다. 칩은 기본적으로 사각형이므로 원형 웨이퍼를 패키징하면 외곽 부분은 폐기해야 한다. 하지만 기판이 사각형이면 버리는 부분 없이 더 많이 패키징할 수 있기 때문에 원감절감에 유리하다. 기판이 크기 때문에 한번에 패키징되는 칩의 수도 월등히 많다. FO-WLP의 사용비율(Usage ratio)이 85% 수준이라면, FO-PLP는 95% 수준이다.

◇열에 따른 몰딩 변형, 패널 휘어짐 난제 직면

이론적으로 네패스의 FO-PLP는 FO-WLP를 기술적으로 앞지를 수 있는 공정으로 평가된다. 하지만 문제는 공정 난이도다. FO-PLP는 패키징하려는 칩을 보호하기 위해 고무 재질의 몰딩을 씌우는데, 이 몰딩이 열에 약해 공정상에서 변형되는 한계를 노출한다. 여기에 대형 기판을 사용하다보니 패널이 열을 받아 휘어지는 현상도 번번이 발생했다. 기판의 휨 현상을 잡지 못하면 배선 불량이 다량 발생해 수율에 치명적인 영향을 미친다. 업계의 말을 종합하면 네패스는 열과 관련된 수율 문제를 해결하지 못했다.

후공정 업계 한 관계자는 "현재 패키징 시장에서는 FO-PLP 방식을 폭넓게 적용하는 단계가 아닌데다 아직까지도 시장 수요가 나오지 않고 있다"면서 "삼성전자는 결과적으로 SiP(시스템 인 패키지)를 하려고 PLP 방식을 띄운건데 네패스가 수율을 잡지 못하면서 결과적으로 애매한 그림이 그려졌다"고 말했다. SiP는 여러 개별 칩을 단일 패키지에 결합하는 패키지 기술이다.

모바일 AP 시장을 장악하고 있는 퀄컴(스냅드래곤)은 올 2분기 네패스그룹(네패스라웨)과 체결했던 공급계약을 해지하는 결정을 내렸다. 상대적으로 저가인 PMIC(전력반도체) 물량을 일부 수주하면서 SoC(시스템온칩) 양산 수주의 기대감을 높였으나 결과적으로 기술적 난제를 잡지 못하면서 대형 고객사인 퀄컴을 놓친 셈이다. 퀄컴은 현재 ASE에 패키지를 맡기고 있다. 이 여파로 FO-PLP 부문을 이끌던 핵심 개발인력들이 대거 정리되는 등 한바탕 홍역을 치렀다는 전언이다.

업계 관계자는 "퀄컴 관련 마케팅을 진행하던 미국법인(Nepes US)도 정리수순인 걸로 알고 있다"고 전했다.

< 저작권자 ⓒ 자본시장 미디어 'thebell', 무단 전재, 재배포 및 AI학습 이용 금지 >

best clicks

최신뉴스 in 전체기사

-

- 수은 공급망 펀드 출자사업 'IMM·한투·코스톤·파라투스' 선정

- 마크 로완 아폴로 회장 "제조업 르네상스 도래, 사모 크레딧 성장 지속"

- [IR Briefing]벡트, 2030년 5000억 매출 목표

- [i-point]'기술 드라이브' 신성이엔지, 올해 특허 취득 11건

- "최고가 거래 싹쓸이, 트로피에셋 자문 역량 '압도적'"

- KCGI대체운용, 투자운용4본부 신설…사세 확장

- 이지스운용, 상장리츠 투자 '그린ON1호' 조성

- 아이온운용, 부동산팀 구성…다각화 나선다

- 메리츠대체운용, 시흥2지구 개발 PF 펀드 '속전속결'

- 삼성SDS 급반등 두각…피어그룹 부담 완화