[반도체 패키징 시대, 삼성의 대응]AVP사업팀 만들고, 이재용 직접 챙긴다①조단위 자금 투입, TSMC 엔지니어 스카웃…양과 질 동반 상승 초점

김도현 기자공개 2023-11-10 12:38:40

[편집자주]

반도체 집적도가 극한에 달하면서 2년마다 성능이 2배 증가한다는 '무어의 법칙'이 계속되지 못할 것이라는 의견이 지배적이다. 업계에서는 노광·증착 등 전공정에서 패키징과 같은 후공정으로 시선을 돌려 반도체의 진화를 이어가고 있다. 삼성전자는 선제적 대응에 나선 TSMC, 인텔 대비 한발 뒤처진다는 평가를 받는다. 다소 출발이 늦은 만큼 총력전 모드로 반전의 계기를 마련할 계획이다. 삼성전자 패키징 부문의 현주소와 가능성을 살펴본다.

이 기사는 2023년 11월 09일 10시04분 thebell에 표출된 기사입니다

"어려운 상황이지만 인재 양성과 미래 기술 투자에 조금도 흔들림이 있어서는 안 된다." 이재용 삼성전자 회장이 지난 2월 충남 천안·온양캠퍼스를 방문하면서 한 말이다. 해당 사업장은 반도체 후공정을 담당하는 곳으로 여기서 이 회장이 언급한 '미래 기술'은 첨단 패키징으로 읽힌다.반도체 산업은 바야흐로 후공정 시대다. 그동안 노광, 식각, 증착 등 전공정 단계에서 회로 패턴 및 선폭을 개선해왔다면 물리적 한계 구간에 진입하면서 단기간 내 반도체 성능을 끌어올리기 어려워졌다.

이같은 상황에서 반도체 제조사는 과거 상대적으로 중요하게 여기지 않았던 패키징 등 후공정에 집중하기 시작했다. 여러 칩을 잘 엮고 잘 쌓아 차세대 반도체를 만들어내기 위함이다.

세계적인 흐름에 삼성전자도 동참했다. 자체 생산하는 메모리반도체와 위탁생산(파운드리)하는 시스템반도체 모두 패키징 기술력을 통해 전반적인 역량을 높이겠다는 취지다.

◇첨단 패키징 전문조직 신설

시장조사기관 가트너에 따르면 반도체 패키징 시장 규모는 매년 5%씩 증가하고 있다. 지난 2023년 574억달러(약 75조원)에서 2027년 1147억원(약 150조원)으로 커지는 수준이다. 특히 첨단 패키징으로 한정하면 연평균 25%의 성장률이 예상된다.

사실 삼성전자는 대만 TSMC, 미국 인텔 등 최선단 반도체 공정을 두고 경쟁하는 회사들보다 후공정에 대한 본격적인 투자가 늦었다. 워낙 사업 영역이 넓은데다 내부 인력 구성이 전공정에 초점이 맞춰져 있기 때문이었다. 이는 국내 반도체 후공정 생태계의 더딘 확장으로 이어졌다. 실제로 대만과 미국에는 유수의 외주반도체조립테스트(OSAT) 회사들이 즐비하다.

상황을 뒤바꾸기 위해 삼성전자는 지난해 6월 후공정을 총괄하는 테스트앤시스템패키지(TSP) 조직 내 어드밴스드패키징(AVP) 태스크포스(TF)를 꾸린데 이어 12월 정식 팀으로 승격시켰다. 올해 1월부터 TSP 조직과 별도로 AVP사업팀이 운영되고 있는 배경이다.

삼성전자는 AVP사업팀에 대해 "인공지능(AI), 서버, 데이터센터, 그래픽과 같은 최고 사양을 요구하는 고객 요구에 맞춰 메모리와 파운드리 사업부에서 생산한 웨이퍼를 바탕으로 어드밴스드패키지 제품을 제공하고 있다"며 "최근 여러 기업이 미세공정 한계를 돌파하기 위해 어드밴스드패키지 기술에 주목하는 시점에서 디바이스솔루션(DS)부문도 해당 분야에 집중하기 위해 AVP사업을 신설하고 고사양 패키징 개발·양산·테스트·출하 전 과정을 담당하고 있다"고 설명했다.

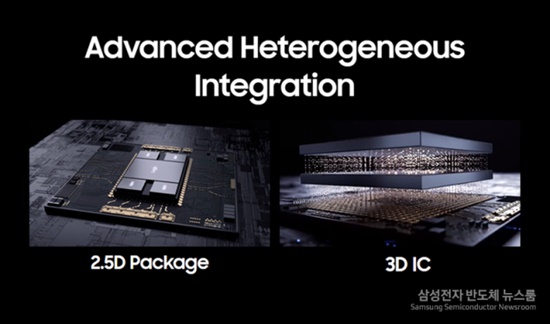

구체적으로 어드밴스드패키지는 메모리 또는 로직 단품의 웨이퍼를 각 칩으로 분리하고 적층해 외부와 전기적 신호를 연결하는 기존 패키징에서 더 나아가 메모리와 로직을 직접 연결해 하나의 시스템을 구현하는 이종(헤테로지니어스)집적 기술이다.

독립적으로 제작한 여러 칩을 연결해 블록처럼 조립하는 '칩렛'과 수직 구조의 '3차원(D)' 및 메모리와 시스템반도체를 수평으로 배열하는 '2.5D' 패키징 등이 대표적이다. 최근에는 웨이퍼와 웨이퍼를 적층하는 '웨이퍼 투 웨이퍼(W2W)', 웨이퍼 전면과 후면을 모두 활용하는 후면전력전달네트워(BSPDN) 등도 떠오로는 기술이다.

AVP사업팀을 앞세워 패키징 고도화에 나서는 한편 삼성전자는 연구개발(R&D) 및 생산능력(캐파) 투자도 단행 중이다. 우선 삼성전자는 경기 기흥캠퍼스에 차세대 반도체 R&D 단지를 구축하고 있다. 이곳에는 2030년까지 약 20조원이 투입되는 가운데 고급 패키징 관련 시설도 마련되는 것으로 전해진다. 지난달 이 회장이 직접 찾을 정도로 중요성이 부각된다.

일본 요코하마에는 수천억원을 투자해 첨단 반도체 개발 거점을 세울 계획이다. 현지에 시제품 라인이 들어설 예정인데 일본 후공정 소재·부품·장비(소부장) 협력사와의 협업이 골자다.

첨단 패키징 거점인 천안공장에서는 캐파 확장에 나선다. 고대역폭메모리(HBM) 제조 과정에서 D램을 수직으로 쌓고, HBM을 인공지능(AI) 반도체와 나란히 배치할 때 필요한 장비를 조단위로 구매해 관련 물량에 대응할 방침이다. 이달 삼성디스플레이 천안사업장 내 일부 거물과 설비 등을 105억원에 사들인 것도 같은 맥락이다.

◇자체 패키징 브랜드 구축, 인재 영입 계속

삼성전자는 TSMC의 칩스온웨이퍼온서브스트레이트(CoWoS), 인텔의 임베디드멀티다이브릿지(EMIB) 등과 맞대결할 2.5D 패키징인 '아이큐브(I-Cube)'를 브랜딩해 고도화하고 있다. 3D 스태킹 패키징인 '엑스큐브(X-Cube)'와 함께 첨단 패키징 라인업을 넓혀나가는 흐름이다.

삼성전자 관계자는 "칩렛 구현을 위해 첨단 패키징 기술 확보에 주력하고 있다"며 "아이큐브에 HBM 탑재 수량을 늘리고, 엑스큐브 검증을 진행하는 등 구체적인 노력이 이뤄지는 단계"라고 설명했다.

양산에 돌입한 최신 애플리케이션프로세서(AP) '엑시노스2400'에 도입한 팬아웃(FO)-웨이퍼레벨패키지(WLP), 다양한 제품에 적용 준비 중인 FO-패널레벨패키지 등도 최적화를 진행 중이다. FO-WLP는 이름 그대로 입출력(I/O) 단자를 바깥으로 빼서 웨이퍼 단위로 칩을 포장하는 기술이다. FO-PLP는 웨이퍼에서 자른 칩을 사각형 모양 패널에 배치해 패키징하는 기법이다.

아울러 인력 구성에도 공을 들이고 있다. 현재 AVP사업팀은 삼성전자 파운드리사업부 소속이던 강문수 부사장이 이끌고 있다. 이례적으로 파운드리 1위 TSMC에서 약 19년 근무한 린준청을 부사장으로 영입하기도 했다.

올해 3월 AVP사업팀에서 반도체 공정 기술, 패키징 개발, 설비 기술 등 부문에서 신입 공채를 진행한 데 이어 8월에는 경력 사원을 채용한 바 있다.

강 부사장은 "반도체를 수평으로, 수직으로 연결하는 2.5D, 3D 기술을 통해 더 작은 반도체 패키지 안에 더 많은 트랜지스터를 집적할 수 있다"면서 "삼성전자는 세계에서 유일하게 메모리, 로직 파운드리, 패키지 사업을 모두 가진 회사다. 이러한 강점을 살려 경쟁력 있는 제품을 제공할 수 있다"고 강조했다.

< 저작권자 ⓒ 자본시장 미디어 'thebell', 무단 전재, 재배포 및 AI학습 이용 금지 >

best clicks

최신뉴스 in 전체기사

-

- KGC인삼공사, 혈당 케어 브랜드 ‘GLPro’ 확장

- [i-point]원영식 오션인더블유 회장, 산불 피해 장애인·주민 후원

- [thebell note]WM의 IB화

- [연기금투자풀 지각변동]ETF 포트폴리오 추가…삼성·미래에셋운용의 '고민'

- [Product Tracker]IMM로즈골드5호 GP커밋, 유동화 펀드 구조는

- 전진건설로봇 기초자산 EB…운용사 우려에도 700억 매듭

- 엘엑스운용 'NPL펀드' 론칭…패밀리오피스 자금 확보

- [스튜어드십코드 모니터]마이다스에셋운용, 적극적 행사기조 '현재진행형'

- ACE 미국500타겟커버드콜, 월배당 매력 '눈길'

- [연기금투자풀 지각변동]하위운용사도 눈치싸움…"증권사 무방 vs 기존 선호"

김도현 기자의 다른 기사 보기

-

- [로보락이 쏘아올린 작은 공] 팔 달린 로봇청소기 등장 '포트폴리오 다변화 속도'

- [Sanction Radar]중국 AI 반도체 옥죄는 트럼프 '삼성·SK 우회로 탐색'

- [삼성 빅딜 리부트]'가전 맞수' 삼성·LG, HVAC 타고 불황 넘는다

- 삼성전자, 갤럭시 엣지 모델 첫 출시 '생산지 분산'

- [Sanction Radar]LG전자, 생산거점 다변화 속도 '인도 투자 강행'

- [삼성그룹 북미 대관조직 분석]강해지는 트럼프 압박, 늘어나는 로비 금액

- [소부장 2세 시대 개막]한미반도체, '오너 3세' 경영수업 본격화될까

- [Company Watch]헥토그룹, 1분기 매출 역대 최대 '전 사업 호조'

- [로보락이 쏘아올린 작은 공]'스마트홈 한축으로 부상' 삼성·애플 기기 연동

- 하나마이크론, 인적분할 믿는 구석 '브라질 법인'