삼성전자, 1b D램 경쟁력 입증 '가장 좁은 회로선폭' 이전 모델 대비 9.13% 축소…하이닉스·마이크론 대비 '우위'

노태민 기자공개 2024-11-14 07:47:57

이 기사는 2024년 11월 12일 15:02 thebell 에 표출된 기사입니다.

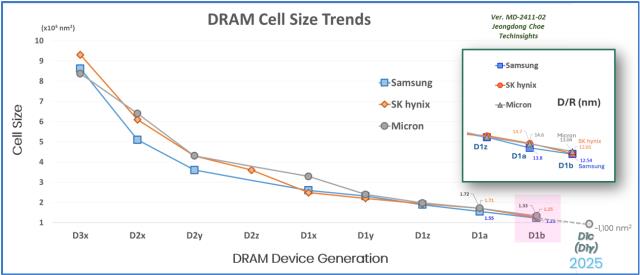

삼성전자의 10nm 5세대 D램(1b D램)이 주요 메모리 기업의 동일 제품 중 회로 선폭이 가장 좁은 것으로 나타났다. 최근 불거지고 있는 기술력 약화에 대한 우려를 불식시킨 셈이다. 업계에서는 차세대 D램 역시 삼성전자가 가장 좁은 회로 선폭을 선보일 것이란 기대가 나온다.리버스엔지니어링 기업 테크인사이츠는 최근 보고서를 통해 삼성전자 1b D램의 회로 선폭이 12.54nm라고 밝혔다. 이전 세대와 비교해 9.13% 줄어든 수치다. 경쟁사인 SK하이닉스와 마이크론의 1b D램의 회로 선폭은 각각 12.65nm, 13.04nm 수준이다. 회로 선폭 측정에는 주사전자현미경(SEM)과 투과전자현미경(TEM)이 함께 사용됐다.

회로 선폭은 반도체 성능을 나타내는 핵심지표 중 하나다. 선폭이 좁을 수록 트랜지스터의 집적도를 높일 수 있기 때문이다. 트랜지스터 집적도를 높이면 반도체의 성능과 전력 효율을 향상시킬 수 있다. 반도체 기술 발전도 회로 선폭을 줄이는 방향으로 흘러왔다. 내년 본격 양산될 것으로 예상되는 1c D램의 회로 선폭은 11nm 대로 줄어들 것으로 기대된다.

비메모리 회로 선폭 축소 속도는 더욱 빠르다. 삼성전자, TSMC 등 파운드리 기업들은 현재 3nm 반도체를 생산 중이며, 내년 2nm 반도체 양산을 앞두고 있다. 삼성전자의 갤럭시 워치 7에 탑재된 웨어러블용 프로세서 엑시노스 W930이 3nm 공정으로 만들어진 반도체다.

삼성전자가 경쟁사 대비 미세한 회로 선폭을 구현할 수 있었던 배경에는 선제적으로 도입한 극자외선(EUV) 공정이 있었다. 2020년 업계에서 가장 먼저 D램 생산 공정에 EUV 장비를 도입했다.

EUV 장비는 반도체 웨이퍼에 회로를 새기는 포토 공정에 활용되는 장비다. 미세 회로 선폭 구현을 위한 필수 장비다. 반면 SK하이닉스는 1a D램부터 EUV 공정을 적용했으며, 마이크론은 1c D램부터 EUV 공정을 도입할 예정이다.

D램 업계 관계자는 "삼성전자 D램의 경우 SK하이닉스나 마이크론과 비교해 EUV 레이어 수가 많다"며 "이러한 부분이 회로 선폭 미세화에 도움이 된다"고 말했다. 이어 "다만 EUV 레이어를 늘리면서 D램 원가 경쟁력에는 열세를 보이고 있는 상황"이라고 부연했다.

테크인사이츠는 1c D램에서도 삼성전자의 회로 선폭이 가장 좁을 것으로 전망했다. 최정동 테크인사이츠 수석부사장은 "삼성전자가 곧 출시할 1c D램 회로 선폭은 업계 최초로 11nm 이하가 될 것"이라고 설명했다. 삼성전자는 1c D램을 고대역폭메모리(HBM), GDDR, LPDDR, DDR 등에 활용할 예정이다.

< 저작권자 ⓒ 자본시장 미디어 'thebell', 무단 전재, 재배포 및 AI학습 이용 금지 >

best clicks

최신뉴스 in 인더스트리

-

- [북미 질주하는 현대차]윤승규 기아 부사장 "IRA 폐지, 아직 장담 어렵다"

- [북미 질주하는 현대차]셀카와 주먹인사로 화답, 현대차 첫 외국인 CEO 무뇨스

- [북미 질주하는 현대차]무뇨스 현대차 사장 "미국 투자, 정책 변화 상관없이 지속"

- [IR Briefing]벡트, 2030년 5000억 매출 목표

- [i-point]'기술 드라이브' 신성이엔지, 올해 특허 취득 11건

- "최고가 거래 싹쓸이, 트로피에셋 자문 역량 '압도적'"

- 한컴이노스트림, '도장 인식 시스템' 특허 취득

- [클라우드 키플레이어 MSP 점검] '신생' 안랩클라우드메이트, 최우선 과제 '포트폴리오 강화'

- 나우어데이즈 신곡 '렛츠기릿', 주요 음원차트 진입

- 유연성·독립성 갖춘 코웨이 코디, 시공간 제약 없어 'N잡' 가능 눈길

노태민 기자의 다른 기사 보기

-

- LG이노텍 인사, 주력 광학솔루션사업 힘싣기 '선명'

- '하이닉스 아픈 손가락' SK키파운드리, 가동률 70%↑

- [삼성 vs SK 메모리 투자 전략] '메모리 경쟁력 높여라' 차세대 메모리 개발 사활

- [삼성 vs SK 메모리 투자 전략]치킨 게임 옛말, 낸드 소극적 기조 계속된다

- 삼성전기, 비주력 정리…통신·모듈 철수 '공식화'

- [삼성 vs SK 메모리 투자 전략]'돈되는 것만 키운다' 선택과 집중의 시대

- 네패스 자회사 네패스라웨, 대규모 인력 재배치 단행

- 오로스테크놀로지, 우시 생산법인 설립 '해외판로 개척'

- LX세미콘, 연구개발 조직 개편 'VR·AR 공략 강화'

- [삼성 vs SK 메모리 투자 전략]내년 시설 투자 키워드 '테크 마이그레이션'