삼성전자, 1b D램 경쟁력 입증 '가장 좁은 회로선폭' 이전 모델 대비 9.13% 축소…하이닉스·마이크론 대비 '우위'

노태민 기자공개 2024-11-14 07:47:57

이 기사는 2024년 11월 12일 15:02 thebell 에 표출된 기사입니다.

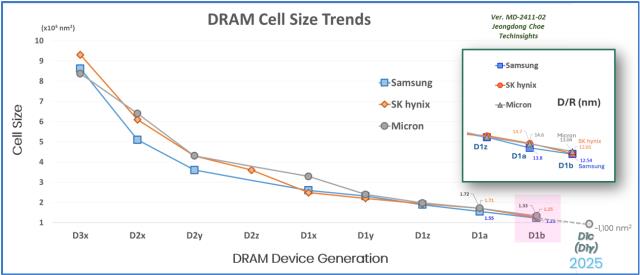

삼성전자의 10nm 5세대 D램(1b D램)이 주요 메모리 기업의 동일 제품 중 회로 선폭이 가장 좁은 것으로 나타났다. 최근 불거지고 있는 기술력 약화에 대한 우려를 불식시킨 셈이다. 업계에서는 차세대 D램 역시 삼성전자가 가장 좁은 회로 선폭을 선보일 것이란 기대가 나온다.리버스엔지니어링 기업 테크인사이츠는 최근 보고서를 통해 삼성전자 1b D램의 회로 선폭이 12.54nm라고 밝혔다. 이전 세대와 비교해 9.13% 줄어든 수치다. 경쟁사인 SK하이닉스와 마이크론의 1b D램의 회로 선폭은 각각 12.65nm, 13.04nm 수준이다. 회로 선폭 측정에는 주사전자현미경(SEM)과 투과전자현미경(TEM)이 함께 사용됐다.

회로 선폭은 반도체 성능을 나타내는 핵심지표 중 하나다. 선폭이 좁을 수록 트랜지스터의 집적도를 높일 수 있기 때문이다. 트랜지스터 집적도를 높이면 반도체의 성능과 전력 효율을 향상시킬 수 있다. 반도체 기술 발전도 회로 선폭을 줄이는 방향으로 흘러왔다. 내년 본격 양산될 것으로 예상되는 1c D램의 회로 선폭은 11nm 대로 줄어들 것으로 기대된다.

비메모리 회로 선폭 축소 속도는 더욱 빠르다. 삼성전자, TSMC 등 파운드리 기업들은 현재 3nm 반도체를 생산 중이며, 내년 2nm 반도체 양산을 앞두고 있다. 삼성전자의 갤럭시 워치 7에 탑재된 웨어러블용 프로세서 엑시노스 W930이 3nm 공정으로 만들어진 반도체다.

삼성전자가 경쟁사 대비 미세한 회로 선폭을 구현할 수 있었던 배경에는 선제적으로 도입한 극자외선(EUV) 공정이 있었다. 2020년 업계에서 가장 먼저 D램 생산 공정에 EUV 장비를 도입했다.

EUV 장비는 반도체 웨이퍼에 회로를 새기는 포토 공정에 활용되는 장비다. 미세 회로 선폭 구현을 위한 필수 장비다. 반면 SK하이닉스는 1a D램부터 EUV 공정을 적용했으며, 마이크론은 1c D램부터 EUV 공정을 도입할 예정이다.

D램 업계 관계자는 "삼성전자 D램의 경우 SK하이닉스나 마이크론과 비교해 EUV 레이어 수가 많다"며 "이러한 부분이 회로 선폭 미세화에 도움이 된다"고 말했다. 이어 "다만 EUV 레이어를 늘리면서 D램 원가 경쟁력에는 열세를 보이고 있는 상황"이라고 부연했다.

테크인사이츠는 1c D램에서도 삼성전자의 회로 선폭이 가장 좁을 것으로 전망했다. 최정동 테크인사이츠 수석부사장은 "삼성전자가 곧 출시할 1c D램 회로 선폭은 업계 최초로 11nm 이하가 될 것"이라고 설명했다. 삼성전자는 1c D램을 고대역폭메모리(HBM), GDDR, LPDDR, DDR 등에 활용할 예정이다.

< 저작권자 ⓒ 자본시장 미디어 'thebell', 무단 전재, 재배포 및 AI학습 이용 금지 >

best clicks

최신뉴스 in 전체기사

-

- 에코프로파트너스, 공정위 ‘경고’…펀드레이징 영향은

- 우리기술, 원전 독점기술 기반 SMR 분야 '첫 수주'

- 금양인터, 펜폴즈 설립 180주년 기념와인 출시

- [Company Watch]큐알티, 'HBM·TEM' 효과 실적 회복세

- [i-point]휴마시스, 짐바브웨 리튬 함유 페크마타이트 광상 스케치 착수

- [i-point]한컴, B2B·B2G 대상 실증사업 박차

- [K-파이낸스 홍콩 IR 2024]원종규 코리안리 대표 "의도된 국내 점유율 하락, 해외에서 성장"

- [반환점 돈 진옥동 체제]후반전 시작, 남은 과제는

- [보험사 할인율 영향 점검]MG손보, 가용자본 급감에 적정성 비율 50%마저 하회

- [캐피탈사 CEO 연임 레이스]김병희 iM캐피탈 대표, 유연한 포트폴리오 전략 성과는

노태민 기자의 다른 기사 보기

-

- [삼성 vs SK 메모리 투자 전략]'돈되는 것만 키운다' 선택과 집중의 시대

- 네패스 자회사 네패스라웨, 대규모 인력 재배치 단행

- 오로스테크놀로지, 우시 생산법인 설립 '해외판로 개척'

- LX세미콘, 연구개발 조직 개편 'VR·AR 공략 강화'

- [삼성 vs SK 메모리 투자 전략]내년 시설 투자 키워드 '테크 마이그레이션'

- 삼성전자, 1b D램 경쟁력 입증 '가장 좁은 회로선폭'

- 이수페타시스, 제이오 인수 시너지? 증권가 '글쎄'

- [트럼프 대통령 재집권]미국 팹리스, TSMC 의존도 낮추기 들어가나

- [트럼프 대통령 재집권]삼성·SK, 중국 팹 운영 비상…공정 전환 차질 우려

- 비메모리 꺾인 삼성전자, 파운드리 협력사들 '한숨'