삼성전자, '1000단' 낸드 청사진 내놨다 웨이퍼 4장 쌓는 '멀티 BV' 낸드 구조, 2030년 개발 목표

노태민 기자공개 2025-02-25 13:07:03

이 기사는 2025년 02월 24일 11시31분 thebell에 표출된 기사입니다

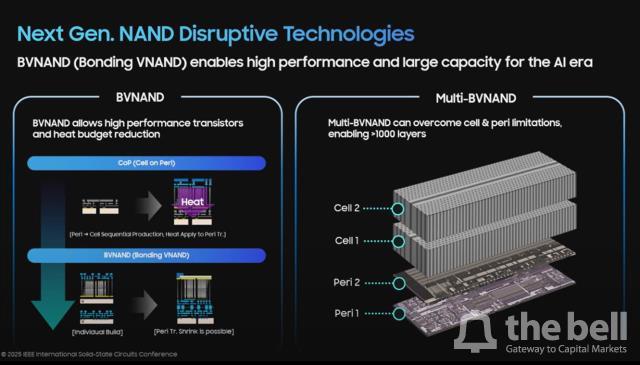

삼성전자가 1000단급 낸드 개발을 위한 제품 구조도를 공개했다. 지난해 공개한 본딩 버티컬(BV)낸드의 업그레이드 버전이다. 구조적 한계를 돌파하기 위해 4장의 웨이퍼를 적층한 점이 눈에 띈다.이를 위한 요소 기술도 대거 적용한다. 웨이퍼 본딩, 극저온 식각, 몰리브덴 적용 등이 대표적인 사례다. 이러한 기술들은 400단급 낸드부터 활용될 예정이다.

◇1000단 낸드 구현 비밀병기, '웨이퍼 본딩'

24일 업계에 따르면 송재혁 삼성전자 DS부문 최고기술책임자(CTO) 사장은 지난주 미국 샌프란시스코에서 열린 국제고체회로학회(ISSCC) 기조연설에서 "본딩 기술을 이용해 (낸드 영역에서) 1000개 이상의 레이어를 구현할 수 있다"고 말했다.

송 사장은 이날 발표에서 1000단 낸드 구현을 위한 멀티 BV 낸드 구조를 공개했다. 2장의 페리 웨이퍼에 2장의 셀 웨이퍼를 적층한 형태다. 이러한 구조를 연구 중인 것은 삼성전자뿐 만이 아니다. 글로벌 낸드 2위 기업 키오시아(KIOXIA)도 멀티 스택 CBA(CMOS directly Bonded to Array)라는 이름으로 연구를 진행 중이다.

삼성전자는 먼저 차세대 낸드(V10)부터 웨이퍼 본딩을 적용한다. 페리페럴(페리) 웨이퍼와 셀 웨이퍼를 각각 만든 뒤, 웨이퍼 본딩으로 연결해 하나의 반도체로 만드는 컨셉이다. 삼성전자 내부에서는 BV낸드라고 부른다. 중국 YMTC는 이 기술을 '엑스태킹(Xtacking)'이라는 이름으로 명명하고 100단 이하 제품부터 적용 중이다. YMTC는 현재 270단급 낸드(페리+셀 웨이퍼, 셀 웨이퍼)를 양산 중이다.

낸드 기업들이 웨이퍼 본딩 기술을 적용하는 이유는 낸드 단수가 높아지면서 한 장의 웨이퍼에 셀과 페리를 모두 구현하는 것이 한계에 다다라서다. 현재 낸드 양산 공정에서의 가장 큰 이슈는 셀을 쌓는 과정에서의 페리 손상이다.

업계에서는 셀만 구현했을 때 하나의 웨이퍼에 쌓을 수 있는 낸드 레이어가 대략 500단 수준인 것으로 보고 있다. 삼성전자가 공언한 1000단 낸드 구현을 위해서는 복수의 웨이퍼 활용이 불가피하다는 이야기다. 삼성전자는 지난 2022년 미국 실리콘밸리에서 열린 '삼성 테크 데이 2022'에서 2030년까지 1000단 낸드를 개발하겠다고 밝힌 바 있다.

삼성전자가 이날 공개한 BV 낸드 컨셉을 살펴보면 셀 웨이퍼를 2장 적층한 것 외에도 페리 웨이퍼를 2장 적층한 것이 눈에 띈다. 이를 통해 고객사의 커스터마이징 수요에 대응할 수 있을 것으로 기대된다.

◇낸드 혁신 지속, 극저온 식각·몰리브덴 요소 기술 대거 적용

삼성전자와 SK하이닉스는 차세대 낸드 개발을 위해 웨이퍼 본딩 외에도 극저온 식각, 몰리브덴 증착 등 신기술을 대거 준비 중이다.

극저온 식각은 400단 이상의 낸드 채널홀 식각에 사용될 것으로 전망되는 차세대 기술이다. 글로벌 반도체 장비 기업인 도쿄일렉트론(TEL)과 램리서치가 관련 장비를 개발·출시를 준비 중이다. 극저온 식각 장비의 가장 큰 특징은 매우 낮은 온도에서 고속으로 식각이 진행된다는 점이다. 이를 통해 낸드 식각 시 스택을 줄일 수 있다는 장점이 있다. 삼성전자는 TEL 장비를, SK하이닉스는 램리서치 장비를 주력으로 활용할 계획인 것으로 파악된다.

워드라인 소재도 변경한다. 기존에는 텅스텐(W)과 질화티타늄(TiN)을 몰리브덴(Mo)으로 변경한다. 이를 통해 트랜지스터 내 '비저항'을 대폭 낮출 수 있다.

메모리 업계 관계자는 "텅스텐을 통해 줄일 수 있는 층고의 한계에 도달했다"며 "몰리브덴을 사용하면 이를 30~40% 줄일 수 있다"고 말했다. 이 시장에서도 TEL과 램리서치가 경쟁 중인 것으로 확인된다. 램리서치는 삼성전자에 복수의 몰리브덴 증착 장비를 이미 공급했으며, TEL도 장비 공급을 준비 중인 것으로 전해진다.

소재 업계 관계자는 "신기술이 적용됨에 따라 장비 시장에 이어, 소재 시장에서도 대격변이 예상된다"며 "차세대 낸드부터 프리커서뿐 아니라 식각액, 모멘텀 가스 등이 대거 변경될 것"이라고 전망했다.

◇차세대 D램·낸드, 로직 공정 적용 '초읽기'

업계에서는 이에 따라 로직 공정의 중요도가 더욱 높아질 것으로 전망하고 있다. 페리와 셀을 분리해서 생산하는 만큼 페리 웨이퍼 양산은 성능이 더 높은 로직 공정을 활용할 확률이 높아서다.

고대역폭메모리(HBM)가 대표적인 사례다. HBM은 HBM3E까지 D램 공정을 이용해 베이스 다이 생산을 진행했으나 HBM4부터는 파운드리 공정을 이용해 베이스 다이를 양산한다. 삼성전자는 자체 파운드리 공정을, SK하이닉스는 TSMC 파운드리를 이용한다.

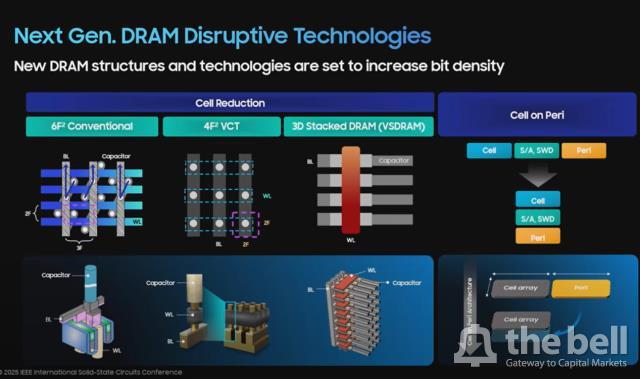

이러한 움직임은 D램에서도 관측된다. 삼성전자와 SK하이닉스 등 기업들은 10nm 미만 D램(0a D램)부터 페리 웨이퍼에 핀펫(FinFET) 공정을 적용한다는 계획이다. 핀펫 공정 기술력이 없는 SK하이닉스는 지난해 핀펫 경력사원을 대거 채용하기도 했다.

메모리 업계 관계자는 "페리와 셀을 나눠서 생산하면서 페리 생산의 유연성이 올라갔다"며 "용처에 따라 페리 웨이퍼를 선단 공정을 통해 생산할 수도 있다"고 설명했다. 이어 "D램의 경우 0a부터 핀펫 공정을 활용할 확률이 높다"며 "삼성전자와 SK하이닉스 모두 관련 연구를 진행 중"이라고 부연했다.

< 저작권자 ⓒ 자본시장 미디어 'thebell', 무단 전재, 재배포 및 AI학습 이용 금지 >

best clicks

최신뉴스 in 인더스트리

-

- [i-point]케이쓰리아이, 아시아 첫 '볼로냐 라가치 크로스미디어상'

- 글로벌사업 중심축 두산밥캣, '5세 경영수업' 무대됐다

- [다시 돌아온 초록뱀 그룹]전방위 영토확장, 이번엔 가상자산 간접투자 단행

- 'EUV PR 국산화 큰별' 이부섭 동진쎄미켐 회장 별세

- [Red & Blue]한빛레이저, 로봇 배터리에 유리기판까지 '겹호재'

- 두산가 5세 '경영 수업' 속도...박상수 두산밥캣, 박상우 ㈜두산행

- '또 불거진' 한국GM 철수설, 현대차 손잡고 불식시킨다

- [배당정책 리뷰]현대글로비스, 무상증자 후 첫 배당…'배당성향 25%' 벽 넘었다

- [i-point]채비, 미국 윌리엄슨 카운티 경제개발청과 LOI 체결

- [i-point]아티스트유나이티드, 한한령 해제 기대감

노태민 기자의 다른 기사 보기

-

- 'EUV PR 국산화 큰별' 이부섭 동진쎄미켐 회장 별세

- 삼성전자, '1000단' 낸드 청사진 내놨다

- [세미콘코리아 2025 리뷰]삼성·SK, 낸드 '웨이퍼 본딩' 도입 초읽기

- [세미콘코리아 2025 리뷰]최창식 DB하이텍 부회장 "SiC 반도체 샘플 곧 공급"

- 삼성전자, '엑시노스 2500' 양산 시작

- [세미콘코리아 2025 리뷰]반도체 '결합' 다 잡는다, 삼성·SK 전자빔 장비 활용

- 체리피커와 한국 팹리스

- 삼성전자, 차세대 로직 기술 '3DSFET' 개발 중

- [세미콘코리아 2025 리뷰]삼성전자, V11서 쿼드러플 스택 적용 '낸드 리더십 강화'

- [세미콘코리아 2025 리뷰]동진쎄미켐, 차세대 PR 'MOR' 올해 내 샘플 공급