삼성전자, 차세대 로직 기술 '3DSFET' 개발 중 0.5nm 공정서 적용 예상, 2030년 이후에야 상용화

노태민 기자공개 2025-02-20 07:37:27

이 기사는 2025년 02월 18일 18시07분 thebell에 표출된 기사입니다

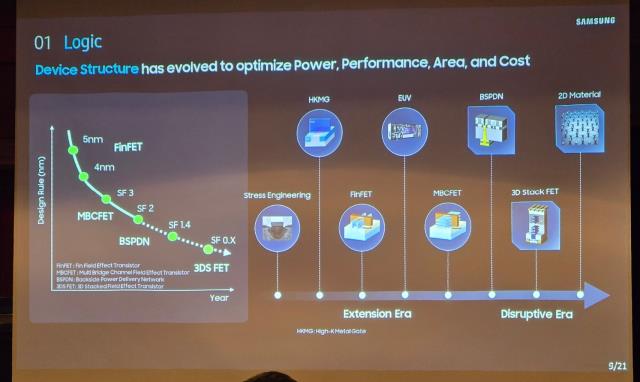

삼성전자가 차세대 소자 기술로 3DSFET을 개발 중이다. 3DSFET은 상보형전계효과트랜지스터(CFET)로도 불리는 기술로 1nm 미만 미세 공정에서 적용될 것으로 전망 받는 기술이다.18일 현상진 삼성전자 반도체연구소 부사장(사진)은 Imec 테크놀로지 코리아 2025에서 기자와 만나 "3DSFET을 개발 중"이라고 말했다.

3DSFET은 게이트올어라운드(GAA) 이후 적용될 트랜지스터 구조다. 1nm 미만 파운드리 공정에서 적용될 것으로 예상된다. P-채널 금속 산화물 반도체(PMOS)에 N-채널 금속 산화물 반도체(NMOS)를 적층해 공간 효율성을 높이고 트랜지스터 집적도를 높였다.

삼성전자에서는 현재 반도체연구소에서 R&D를 진행하고 있는 단계다. 파운드리 경쟁사인 TSMC, 인텔 등 기업도 연구 중이다. 공정 적용까지는 상당 기간이 걸릴 것으로 예상된다. 글로벌 반도체 연구소 Imec은 3DSFET이 이르면 2032년 0.5nm 공정에 적용될 것으로 전망했다.

현 부사장은 3DSFET과 미래 메모리 구현을 위해 3D 패터닝, 소재 혁신, 스태킹(하이브리드본딩) 등 기술 혁신이 필요하다고 강조했다.

다만 현 부사장은 3DSFET의 적용 시점에 대해서는 말을 아꼈다. 그는 "(3DSFET가) 1nm 이하 공정에서 적용될 것으로 보인다"며 "(정확한 적용 시점이나 적용 여부에 대해서는) 아직 정해지지 않았다"고 말했다.

이날 행사에는 Imec 행사에는 이재연 SK하이닉스 부사장도 참여했다. 그는 아날로그 컴퓨트 인 메모리(ACiM), 마그네틱 랜덤 액세스 메모리(MRAM) 등 이머징 메모리 기술에 대해 발표했다. ACiM은 메모리 내에서 직접 연산을 수행하는 컨셉이다. 컴퓨팅과 메모리 사이의 경계를 없앤 차세대 인공지능(AI) 반도체로 주목받고 있다.

< 저작권자 ⓒ 자본시장 미디어 'thebell', 무단 전재, 재배포 및 AI학습 이용 금지 >

best clicks

최신뉴스 in 인더스트리

-

- [미술품 증권신고서 분석]아티피오, 투자증권 정정 후 통과…핵심은 '배당소득세'

- [i-point]소룩스 "주가하락 반대매매 탓, 임상·합병 추진 계속"

- [i-point]아이티센 "금 품귀 현상, 조각투자·개인거래 등 대안 주목"

- 무뇨스 현대차 사장, 첫 타운홀 미팅…'3H 청사진' 의미는

- '현대엔지 시공' 신광교 클라우드시티 '반도체 수요 겨냥'

- 에스이인터, ‘젤라또피케’ 브랜드 안착…사업 다각화 순항

- [에이유브랜즈 IPO]무신사 플랫폼 동반성장, 브랜드 발굴 '성공작' 나올까

- [주주총회 프리뷰]주주서한 받은 농심, '기업가치 정상화' 요구 배경은

- [Company Watch]현대지에프홀딩스, 재무 청사진 '순차입금 20% 감축'

- [IR Briefing]이광후 모니터랩 대표 "SaaS 플랫폼 비즈니스 집중"

노태민 기자의 다른 기사 보기

-

- 삼성전자, '엑시노스 2500' 양산 시작

- [세미콘코리아 2025 리뷰]반도체 '결합' 다 잡는다, 삼성·SK 전자빔 장비 활용

- 체리피커와 한국 팹리스

- 삼성전자, 차세대 로직 기술 '3DSFET' 개발 중

- [세미콘코리아 2025 리뷰]삼성전자, V11서 쿼드러플 스택 적용 '낸드 리더십 강화'

- [세미콘코리아 2025 리뷰]동진쎄미켐, 차세대 PR 'MOR' 올해 내 샘플 공급

- [세미콘코리아 2025 리뷰]곽노정 사장 "가성비 AI 모델, 반도체 수요 자극할 것"

- [LX세미콘을 움직이는 사람들]반도체 꿈 잇는 구본준 회장 역할 주목

- SK하이닉스, CXL 컨트롤러 내재화 '칩렛·FOWLP' 도입

- [LX세미콘을 움직이는 사람들]이윤태 대표, 종합반도체의 꿈 '신사업 발굴 총대'