[토종 AI 반도체 생태계 점검]디노티시아, 올해 '개인형 AI 디바이스' 출시⑤VDPU 개발 TSMC 12nm 활용, 2026년 양산

노태민 기자공개 2025-03-19 13:13:04

[편집자주]

글로벌 빅테크 기업 메타가 퓨리오사AI 인수 의향을 내비친 게 큰 화제가 되고 있다. 국내 기술이 글로벌 시장에서 가치를 인정받았다는 점에서 의미가 크다. 자체 AI 반도체 개발을 추진 중이던 메타가 개발 레퍼런스가 있는 한국 기업 인수로 방향을 튼 것이다. 이를 계기로 또 다른 국내 AI반도체 기업들 역시 다시 주목받고 있다. 국내 AI 반도체 기업 생태계와 실체를 살펴본다.

이 기사는 2025년 03월 17일 16시09분 thebell에 표출된 기사입니다

인공지능(AI) 솔루션 기업 디노티시아(Dnotitia)의 사업 전략은 타 AI 반도체, 솔루션 기업과 사뭇 다르다. 디노티시아가 단순 AI 반도체 개발이 아닌 고성능 벡터 데이터베이스(DB) 시스템 사업화를 준비 중이기 때문이다.벡터 DB는 텍스트, 이미지, 동영상 등 멀티모달 데이터를 고차원 벡터로 변환해 유사도 기반 검색을 효율적으로 수행할 수 있도록 설계된 시스템이다.

디노티시아는 자사의 벡터 DB를 가장 잘 활용할 수 있는 방안이 AI 반도체를 직접 개발하는 것이라고 판단했다. 이를 위해 지난해부터 TSMC 파운드리에서 AI 반도체 개발을 진행하고 있다. 올해 내 개인형 AI 디바이스 니모스(Mnemos) 출시도 준비 중이다.

◇자체 개발 '벡터 DB', 토탈 솔루션화 전략

디노티시아는 국내 AI 반도체 기업 사피온 최고기술책임자(CTO) 출신인 정무경(사진) 대표가 2023년 설립한 기업이다. 설립 1년 만에 벡터 DB 시스템 씨홀스(Seahorse) 등을 공개하는 등 빠르게 사업화를 진행 중이다.

정 대표는 국내에서 손꼽히는 AI 반도체 전문가다. 고려대학교 전기공학과 학사를 졸업한 뒤 한국과학기술원(KAIST) 전기및전자공학과에서 석사, 박사 학위를 취득했다. 이후 다이나릿시스템, 한국전자통신연구원(ETRI), 삼성종합기술원 등에서 경력을 쌓았다.

AI 반도체 개발에 본격적으로 뛰어든 것은 SK텔레콤에서부터다. 2020년 신경망처리장치(NPU) X220를 내놨다. X220은 인공지능 반도체 성능 테스트(벤치마크) 대회에서 높은 성능을 인정받아 업계에서 화제를 모았다. 사피온 분사 이후 CTO를 맡게 됐고 제품 개발을 이끌었다.

AI 반도체 업계에서 정 대표의 명성이 상당했던 만큼 디노티시아의 자금조달은 수월하게 진행됐다. 디노티시아는 2023년 10월 140억원 규모 시드 라운드 투자를 시작으로 2024년 9월 프리-A라운드를 통한 180억원 투자금 유치에 성공했다. 또 12월에는 30억원을 추가로 확보해 총 350억원의 투자금액을 유치했다.

디노티시아는 단순 AI 반도체 개발이 아닌 벡터 DB를 이용한 시멘틱 서치(의미기반 검색), 거대언어모델(LLM)을 응용한 솔루션을 준비 중이다. 지난해 11월 벡터 DB 시스템 씨홀스를 공개했다. 씨홀스는 LLM이 동작할 수 있는 정보와 장기기억을 제공하고 대규모 데이터에서 고성능의 시맨틱 써치를 가능하게 한다.

회사는 "이를 통해 사용자가 찾고는 정보와 가장 관련성 높은 결과를 정확하게 찾아낼 수 있다"며 "AI 시스템의 정보 검색 및 활용 성능을 한층 끌어올린다"고 설명했다.

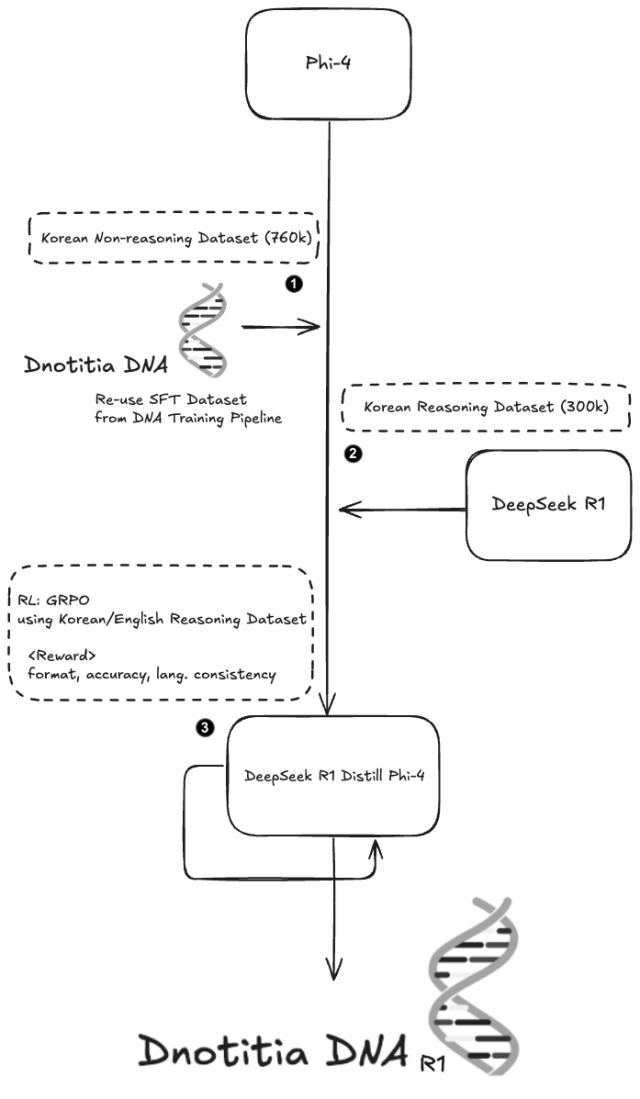

올해 출시 예정인 니모스는 개인형 AI 디바이스다. 벡터 DB와 경량 LLM '디엔에이', AI 반도체 등을 탑재해 데이터센터 연결 없이도 LLM을 활용할 수 있는 것이 특징이다. 회사는 니모스 출시를 통해 본격적인 매출이 발생할 것으로 전망하고 있다.

◇자체 AI 반도체 'VDPU', 2026년 양산

디노티시아는 벡터 데이터 연산에 특화된 자체 AI 반도체도 개발 중이다. 회사 내부에서는 벡터 데이터 프로세싱 유닛(VDPU)라고 부른다. 이를 위해 지난해 TSMC 디자인하우스 에이직랜드와 97억원 규모 '주문형 반도체 설계 개발' 계약도 체결했다.

VDPU 개발 및 양산을 위해 TSMC 12nm 공정을 활용하는 것으로 전해진다. 내년 중 VDPU 테이프아웃을 완료하고 2026년 양산을 예정하고 있다. 테이프아웃은 반도체 설계 마지막 단계다. 설계 도면을 반도체 파운드리에 전달하는 것을 의미한다.

VDPU 개발에는 회사 개발진 외에도 미국 UCSD(강민구 교수팀), 경희대학교(최승규 교수팀) 등이 참여한다. 정 대표는 지난해 VDPU 개발에 대해 "세계 최고 성능의 LLM-RAG 하드웨어-소프트웨어 통합 솔루션을 개발할 것"이라고 자신감을 내비친 바 있다.

< 저작권자 ⓒ 자본시장 미디어 'thebell', 무단 전재, 재배포 및 AI학습 이용 금지 >

관련기사

best clicks

최신뉴스 in 인더스트리

-

- F&F “테일러메이드 우선매수권 행사, 사실무근”

- 스타에스엠리츠, 경영 정상화 위해 매각 추진

- [거래재개 노리는 코스닥사]'위기 속 화해무드' 미디어젠, 경영권 분쟁 일단락 가능성

- [코스닥 어닝 서프라이즈]나인테크, 신소재 양산 시작…장비 넘어 다각화 목표

- [코스닥 어닝 서프라이즈]나인테크, 최대실적 이끈 '이차전지 장비' 효과

- [i-point]아이티센엔텍, 투자주의환기종목 해제

- 대방건설, 공공공사 수주 확대

- [토종 AI 반도체 생태계 점검]디노티시아, 올해 '개인형 AI 디바이스' 출시

- [봄바람 부는 크립토 B2B]밸리데이터 입지 다진 'DSRV', 코인 결제 시장까지 노린다

- [웹툰사 지배구조 점검]디앤씨미디어, IP 확장 초점 '계열사 늘리기'

노태민 기자의 다른 기사 보기

-

- [토종 AI 반도체 생태계 점검]디노티시아, 올해 '개인형 AI 디바이스' 출시

- [thebell interview]조명현 세미파이브 대표 "지난해 매출 1000억 달성"

- DB글로벌칩, 실적 '빨간불' 2년 연속 매출 '역성장'

- '경계현 지우기' 나선 삼성, 파운드리 컨트롤 타워 'CP실' 해체

- [Company Watch]LG CNS, 미국 법인 효자 노릇 '5100억 매출'

- '엑시노스 강화' 삼성전자, 퀄컴서 RF칩 전문가 영입

- '전력반도체' 집중 매그나칩, DDI 사업 매각 추진

- '모바일 HBM' 선점 노리는 삼성전자, '애플'과 개발 협력

- [토종 AI 반도체 생태계 점검]딥엑스, 첫 제품 출하 기대? 매출 5000만원 벽 넘을까

- 삼성전자, 'CXL 3.0' D램 2026년 내놓는다